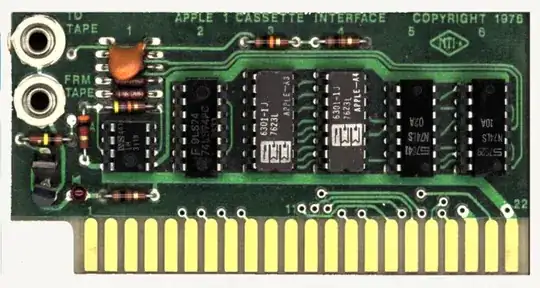

According to this page, the Apple 1 monitor program was located in addresses $F000-$FFFF, a ROM program to use the optional cassette interface card was at addresses $C100-$C1FF, and the peripheral address for writing to the cassette was at $C028.

The most likely explanation is that the address range $C000-$CFFF was reserved for the interface card slot, and that the cassette program was in its own ROM on the interface card. However, it is also possible that there was only one ROM, on the motherboard with both the monitor and cassette programs. Is there evidence documenting how the cassette program was stored?