I'm building a simple Z80 breadboard computer for my hobby. In this question I use Z80 as an example, but I think this may apply to many CPUs that allow for bus sharing.

The problem is as follows. Z80 has a pin called BUSREQ, which after being pulled low, makes the CPU stop it's execution, and float the address, the data and a few control pins to allow for another device to control them. This is an awesome feature I plan to use to program the ROM without having to disconnect/rewire things.

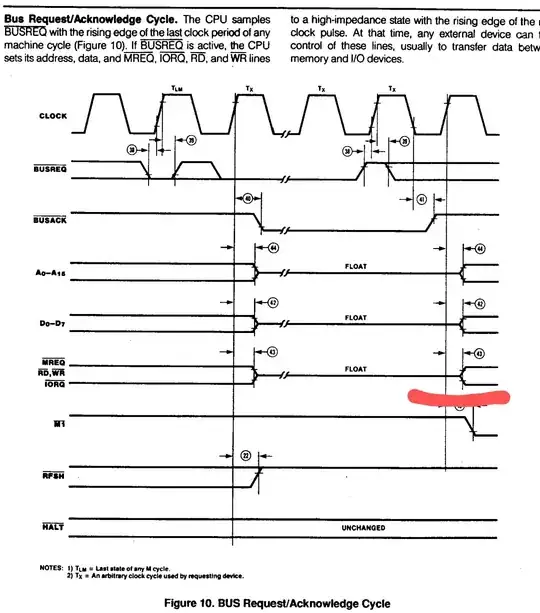

If we take a look at the data sheet, after we pull the BUSREQ pin high again, to give the control back to Z80, we see that after changing BUSACK, confirming that the bus can no longer be controlled, there is a bit of a delay, that I highlighted.

This means, that if my ROM-programmer let's go of the bus like a good citizen, pins will float until the CPU controls them. This is not a big problem for the address and the data, but a pretty serious problem for the WR pin, which controls writing to memory. If I understood correctly, at the end of bus sharing, floating pins have the reign over my memory, potentially overwriting it.

This is especially a problem for me, since for hobby purposes I use a 3hz clock for the setup, making the floating time extremely long.

A solution that I came up with to solve this, is to have a multiplexer controlled by the programmer. The high WR signal would be held a little after BUSACK goes high.

But it keeps bugging me, there must be a better solution than external circuitry? Or maybe it doesn't matter that much? What was the thought in making the lines float that short time after?