I need help in the layout of an ethernet interface (ESD protections + RJ45 connector). The connector I would like to use already has built-in magnets, so I only have to connect the ESD protectors.

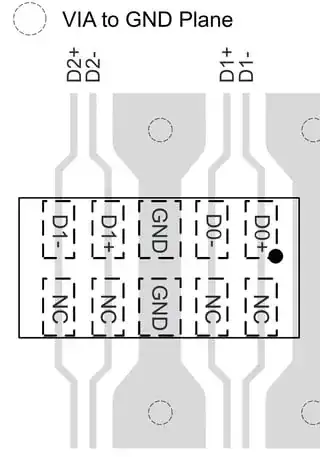

Almost all ethernet ESD protection chips have this package and pinout, see the example the ESDS312DBVR.

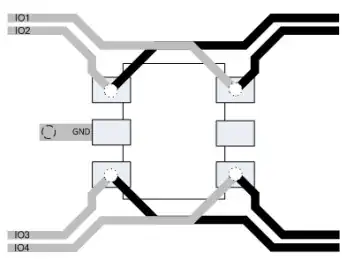

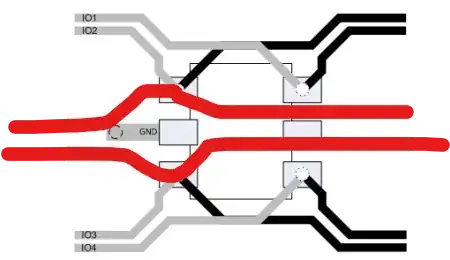

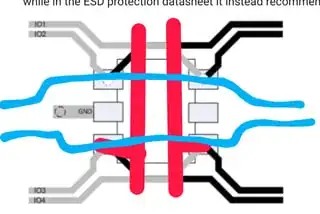

My doubt derives from the fact that in the datasheet of the ethernet controller it is recommended to trace the differential pairs towards the RJ45 connector all on the top layer; while the ESD protection datasheet instead recommends changing the bottom layer:

What would be the most correct way? I think it's best to avoid vias, so do everything on the top layer, but then I'm having trouble connecting ESD protection.

My idea is to use two ESD protection chips, one for the TX pair and one for the RX pair (so using only half a chip and two hips) and going under the chip with the differential pair might be a solution? What do you think? This way: