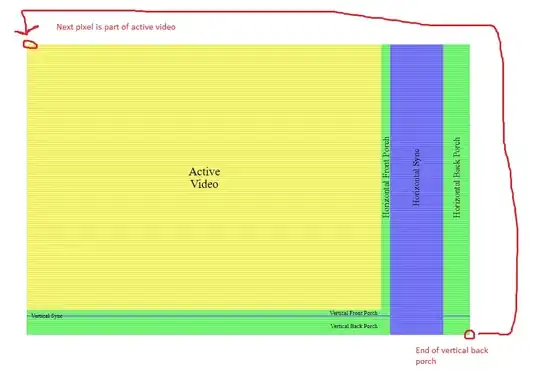

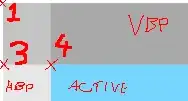

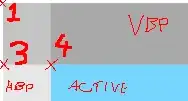

The difference seems to be simply that the (imaginary, externally non-observable) periods of time for the horizontal and vertical porches are counted differently. In the first image, the period between HSYNC and the first active image pixel (3-4) is considered part of the vertical back porch:

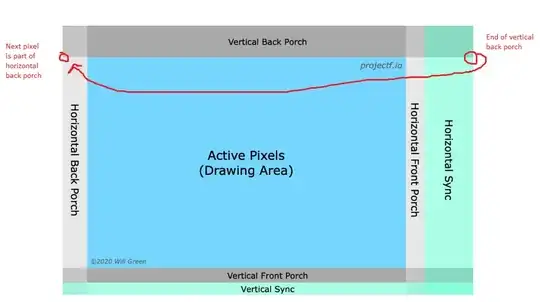

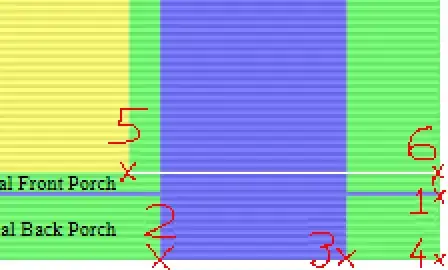

while in the second image that same (equal-length) time period from hsync to first active image pixel (3-4) is considered part of the first line outside of the back porch:

Essentially, the vertical back porch starts, and ends, earlier in the second image. However, the disagreement occurs outside of the active area and sync signals anyway, so there is no real timing discrepancy.

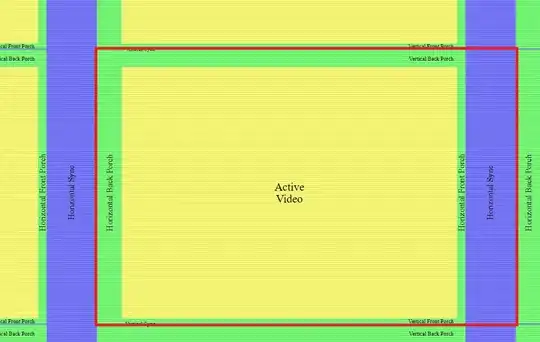

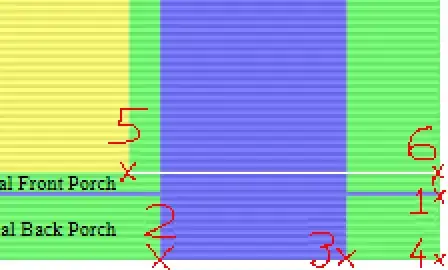

The two images still have an unclear discrepancy with when the VSYNC signal starts and ends, since they don't have enough detail to show relative timing between HSYNC and VSYNC. The ambiguity is whether VSYNC starts with the horizontal back porch, through the end of the vertical back porch, or if it starts at the end of the horizontal back porch and ends at the end of the horizontal sync. On the diagrams, this can be seen as a discrepancy of whether (1) aligns with (3) or with (4).

A few references I looked at (including ones that reproduce diagrams from monitor manuals) also don't show this relationship, and display timings are generally a mess of different competing standards with vague similarities and subtle differences.

I would suspect that because these drive separate sync and counter circuits, that exact relationship doesn't matter as long as the general timings (line-to-line and column-to-column) match up.