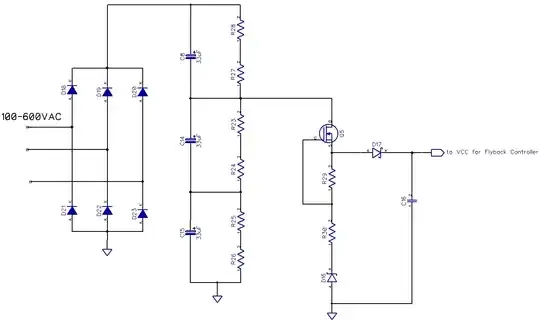

I'm trying to design a startup network for this flyback controller, see the picture at the end. I want the controller to start within 10 ms at most. This is what I'm doing:

Due to the wide input voltage, I'm connecting the startup network to a tapping point from the capacitors in series. This allows me to choose a lower Vds depletion MOSFET like this: CPC3980ZTR

1) Would this cause some imbalance in the caps?

Now, during startup a current flows from inputs caps C14 & C15 through the depletion MOSFET Q5 (normally on). This current will charge the Vcc capacitor C16. The gate of Q5 is connected in the middle of the resistor divider formed by R29 and R30. As the voltage over C16 increases, the gate voltage of Q5 becomes negative with respect to its source voltage. When threshold voltage of Q5 is achieved, it turns off.

Resistors R29 & R30, and Zener diode D16 are dimensioned so that Vcc achieves the minimum value UVLO for the controller to start. From this point, controller will be fed by the auxiliary winding, and Q5 will stay off until the next start-up.

According to the datasheet, the threshold voltage for Q5 has minimum and maximum levels of -3.1 and -1.4, respectively. The minimum Vcc voltage for the controller to start is UVLO = 21V, and the max Vcc is 35V. I will allow a max voltage of 27.5V for overvoltage protection. During startup, the voltage over resistor R29 is the voltage between gate and source of Q5.

- By setting R29 = 10K

- R29*i_R29 < 1.4V only if V_C16 > 19.5V --> i_R29 < 0.140 mA for V_C16 = 19.5V

- R29*i_R29 > 3.1V only if V_C16 < 27.5V --> i_R36 > 0.310 mA for V_C16 = 27.5V

By using a 20V Zener diode as D16, the first condition is met.

For the second condition, the current through R29 can be calculated as

- I_R29 = (V_C16 + V_D17 – V_D16)/(R29+R30)

- R30 < (27.5 + 0.3 – 20)/(0.4mA) – 10K

- R30 < 15.2K

- R30 = 10K

2) How do I calculate a proper value for C16? And the time this circuit will actually take to start the controller?

EDIT: Below there is a potential way of doing it with a known current