simulate this circuit – Schematic created using CircuitLab

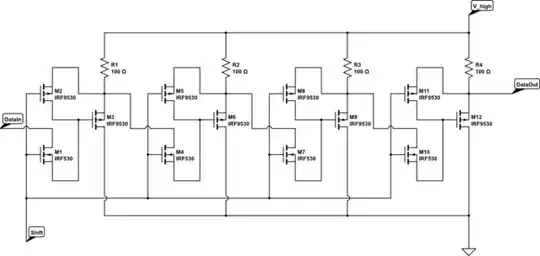

The basic data structure for the machine I want to build is a shift register. Quite some time back someone told me that if I could implement it without a master/slave architecture then I really should. So I came up with the following schematic for a shift register of four bits. I'm banking rather heavily on my ability to time each assertion of (shift) just long enough to move each bit of data from one position to the right, perhaps a little over two transistor delays, and definitely less than three transistor delays.

I may be able to get this to work for four bits, but my machine is going to need a shift register as large as four billion bits long to do what it needs to do. If I extend this schematic to four billion bits, can I realistically expect to be able to assert (shift) long enough to move each of the four billion bits just one position to the right and no further?

This article was marked as a duplicate of another article, and I was told that if I disagreed that it was a duplicate I should edit it to point out why it's not a duplicate. The original article used BJTs instead of MOSFETs. I was told that the output of M1 and M2 couldn't be amplified by M3. I changed all the BJTs to MOSFETs in an attempt to fix that, but nobody commented on the change. So I started this article out with MOSFETs instead of BJTs in order to prompt people to tell me what's wrong with my design, to tell me why it won't work as a shift register. That's the difference from the original article.